|

|

|

www.design-reuse-china.com

www.design-reuse-china.com |

|

OPENEDGES 成功验证7nm HBM3测试芯片

加拿大安大略省马克姆,2024 年 7 月 XX 日 --- 领先的内存子系统 IP 提供商 OPENEDGES Technology, Inc (OPENEDGES) 很高兴地宣布,其子公司 The Six Semiconductor Inc (TSS)已成功推出并验证了其采用 7nm工艺技术的 HBM3 测试芯片。IP 验证测试芯片和 HBM3 PHY 在第一个月内就提升到了 6.4Gbps,进一步的调整使 HBM3 内存子系统成功超频至 7.2Gbps。

Jul. 16, 2024 –

到目前为止,只有少数 IP 供应商已经流片并演示了 HBM3 内存子系统,因为测试流片班车和 HBM3 DRAM 颗粒样品都非常有限。OPENEDGES 很高兴成为少数几家在硅片中展示 HBM3 内存子系统的公司之一。

TSS 首席工程师兼 HBM3 PHY 和测试芯片项目负责人 Farhad Haghighi Zadeh 表示:"我们对经验丰富的工程团队的能力充满信心,这让我们能够承担极具挑战性的 HBM3 PHY IP 和测试芯片开发任务。我们非常高兴能够顺利、成功地推出 HBM3 测试芯片,展现我们的卓越能力。"

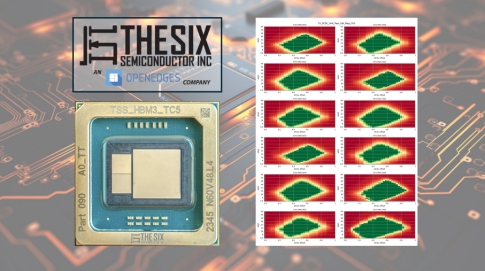

<图1:HBM3为一个64位通道写入schmoo,以7.2Gbps的速度叠加成12个schmoo组>

HBM3 PHY采用最先进的架构,在工艺、电压和温度变化的情况下,最大限度地提高时序和电

压余量,同时最大限度地减少数据流量中断。HBM3 PHY IP 能够支持多达 16 个独立异步通道,每个通道都有 2x32 位 DWORD 伪通道。

其它功能包括快速频率切换(多个频率设定点)、瞬态错误处理(例如 ECC、数据奇偶校验和命令/地址信号),以及通道修复(互连冗余重映射),可在出现互连问题时自动检测、修复和重映射,使这些问题对内存控制器透明。

HBM3 内存子系统的开发与其它传统 DDR 类型的开发有很大不同,因为内存控制器/PHY SoC 与 HBM3 颗粒堆栈、硅中介层和封装基板一起采用2.5D 集成,需要高度的物理架构一致性,以便正确分配、连接和验证数以万计的 SoC 微凸块。因此,需要复杂的物理结构设计来仔细处理跨多个设计层次的相互交织的依赖关系。例如,微凸块阵列分配会影响芯片级的 PHY 布局,就像它会影响硅中介层上的 RDL 布线一样。除此之外,还需要在大量信号中实现稳固的垂直电源和接地传输, 这需要与高速信号布线一起提前规划,而不是事后再考虑。

HBM3 PHY 测试芯片开发中使用的方法非常适合未来的芯粒Chiplet设计。 从信号布线和电源/接地传输的早期物理规划,到凸块和 BGA 球以及封装基板布线和平面的共同规划,再到所需的物理验证和交叉检查。这些只是规划和开发高级内存子系统芯粒Chiplet所需的一些专业知识和实践知识。

凭借其 HBM3 PHY 和测试芯片的硅验证成功、成熟的设计方法和专业知识以及完整的内存子系统 IP 产品组合,OPENEDGES 有望成为芯粒Chiplet领域的首选内存子系统 IP 供应商。

"我们为 HBM3 测试芯片的成功推出和惊人的结果感到非常自豪,这不仅展示了我们执行设计的能力,还展示了我们推出和调整内存子系统以最大程度地提高性能的能力",TSS 首席执行官 Richard Fung 表示,"凭借将最新 DDR 技术引入成熟技术节点的产品开发理念,我们的高级内存子系统 IP 系列非常适合任何希望构建具有内存接口的 IO 芯粒Chiplet的公司。我们的内存控制器和 PHY 完全集成、经过充分验证,可随时部署到客户的芯粒Chiplet产品中。"

OPENEDGES Technology 首席执行官 Sean Lee 表示:"我们的 HBM3 测试芯片成功通过验证不仅是一个里程碑,而且证明了我们技术的价值。我们继续在先进节点验证我们的 IP 方面取得重大进展,

并采取进一步措施为我们的合作伙伴提供卓越的性能和可靠性。"

OPENEDGES 现已正式被列为 Chiplet Marketplace 上的 Chiplet 生态系统 IP 供应商,并准备将其首款 UCIe Chiplet 控制器 IP 推向市场。如需了解更多详情或进行探索性讨论,请通过 sales@openedges.com 与我们联系。

关于Openedges Technology,Inc. OpenEdges Technology,Inc.是半导体行业内存子系统IP的主要提供商。他们提供各种最新的解决方案,包括DDR内存控制器,DDR PHY,NOC InterConnect和NPU IP,这些解决方案已被全球客户广泛采用。他们的IP符合JEDEC标准,包括LPDDR5X/5/4X/4/3,DDR5/4/3,GDDR6和HBM3,以确保它们与最新的DDR技术趋势的兼容性。 2019年,他们收购了The Six Semiconductor,Inc.(TSS),专门从事多种技术的高速PHY。作为韩国证券交易所市场(394280. KQ)的上市公司,OPENEDGES 可以持续增长并保持其在内存子系统IP市场中的领导地位。 通过访问官方网站www.openedges.com了解有关公司及其产品的更多信息。 关于 The Six Semiconductor Inc. (TSS) TSS 是一家加拿大科技公司,也是 OPENEDGES 的全资子公司,专门开发先进的高速 DDR PHY IP 解决方案,以满足 AI/ML、高性能计算 (HPC)、移动设备和汽车等广泛应用的需求。该公司的产品组合包括针对各种内存标准的 PHY IP,包括 LPDDR5x/5/4x/4、GDDR6 和 HBM3,这些 IP 针对功率和面积进行了优化。TSS 的解决方案旨在与多种技术、代工厂和工艺节点兼容。该公司的专家团队在该领域拥有丰富的经验,致力于为行业提供高质量、可靠的 DDR PHY IP 解决方案。 要了解有关 TSS 产品的更多信息,请访问其网站 www.thesixsemi.com

Back

Back